Agnisys Automation Review Anupam Bakshi

Anupam Bakshi is Chief Executive Officer (CEO) for Agnisys, Inc., the pioneer and industry leader in Golden Executable Specification Solutions™. From his early days at Gateway Design Automation, through to his time at Cadence, PictureTel, and Avid Technology, he has been passionate about … More » Specification-Driven UVM Testbench GenerationSeptember 22nd, 2020 by Anupam Bakshi

In February, we will celebrate the tenth anniversary of Accellera approving the first version of the Universal Verification Methodology (UVM). It’s no exaggeration to say that UVM changed the world of semiconductor verification. It wasn’t the first verification methodology, and not even the first to use SystemVerilog, but it was developed and supported by all major electronic design automation (EDA) vendors. Users could write testbenches using the UVM building-block library and its detailed guidelines, secure in the knowledge that simulators and other tools would handle them properly. UVM focused the diverse set of constructs and powerful capabilities available in SystemVerilog on the specific task of building a reusable verification environment. Object-oriented programming (OOP) support meant that users could extend the building blocks without modifying them. Adherence to the guidelines made verification components reusable “horizontally” across projects and even across companies. Passive components such as monitors and coverage collectors, and even some active interface models, could be reused “vertically” from block to subsystem to system.

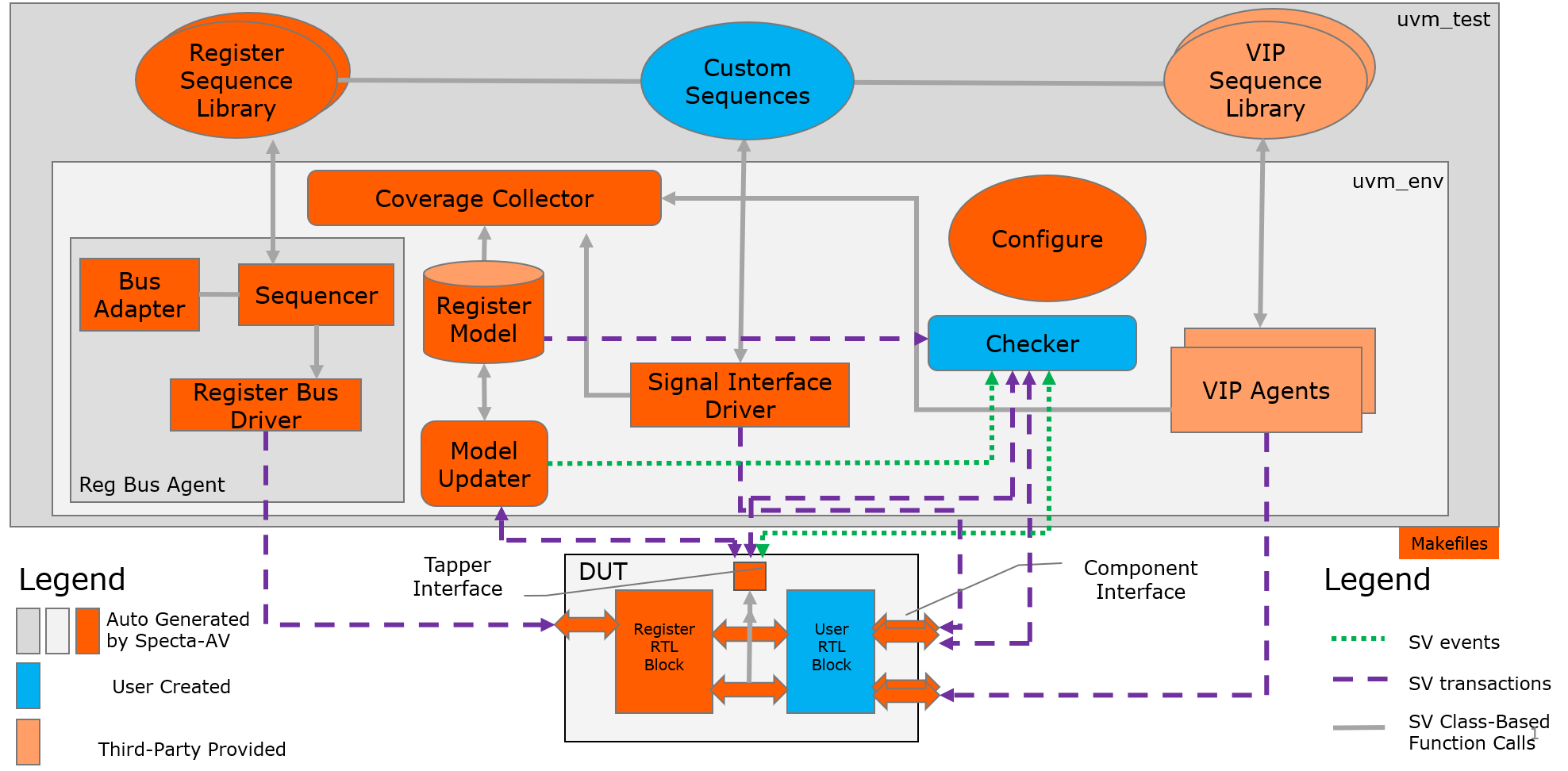

Above all, UVM brought automation to testbenches. Verification engineers no longer had to hand-write tests for every feature in the design. They could set up an environment in which sequencers automatically generated an unlimited number of tests, of any length, with countless variations. Chip verification teams today still enjoy these benefits, but they are not without cost. It takes time and a fair amount of expertise to set up a UVM environment. Since it eliminates a huge amount of manual testing and provides better verification coverage, the up-front investment is clearly worth it. It is interesting to ask whether creation and maintenance of a UVM testbench can be automated to reduce the initial effort, minimize the impact of specification changes, and deliver even more value to the verification team. Unfortunately, there is no solution that can magically transform a natural-language specification into a complete verification environment. However, it turns out that there are many parts of a UVM chip testbench that can be automatically generated from executable specifications. The Specta-AV solution from Agnisys provides these capabilities today.

Given our history of register automation at Agnisys, of course Specta-AV provides a great solution in this domain. Users can specify their registers in any of a wide variety of formats, including IP-XACT, SystemRDL, Microsoft Word and Excel plug-ins, or our customized editor. Specta-AV generates all the testbench components needed to verify the registers themselves, access the registers as part of full-chip verification, and keep the testbench synchronized as values change in the RTL registers. Based on the register specification, Specta-AV generates the complete UVM testbench: bus agents, drivers, adaptors, sequencers, and sequences, as well as the makefiles to build the testbench and run tests using all major simulators. These tests provide 100% functional coverage “out of the box” with register-focused cover groups. Test types include positive and negative (such as ensuring that a read-only register cannot be written), indirect register access, and lock/unlock register sequences. Additional sequences are generated for special types such as shadow, alias, and interrupt registers. Specta-AV provides built-in support for numerous standard buses, including ARM® AXI-Full, AXI-Lite, AHB, AHB-Lite, APB, and Avalon. Users are not limited to these choices; they can also define proprietary buses. The sequence specification format in Excel or Python is exceptionally flexible to accommodate many different types of control flow. Among other attributes, users can specify:

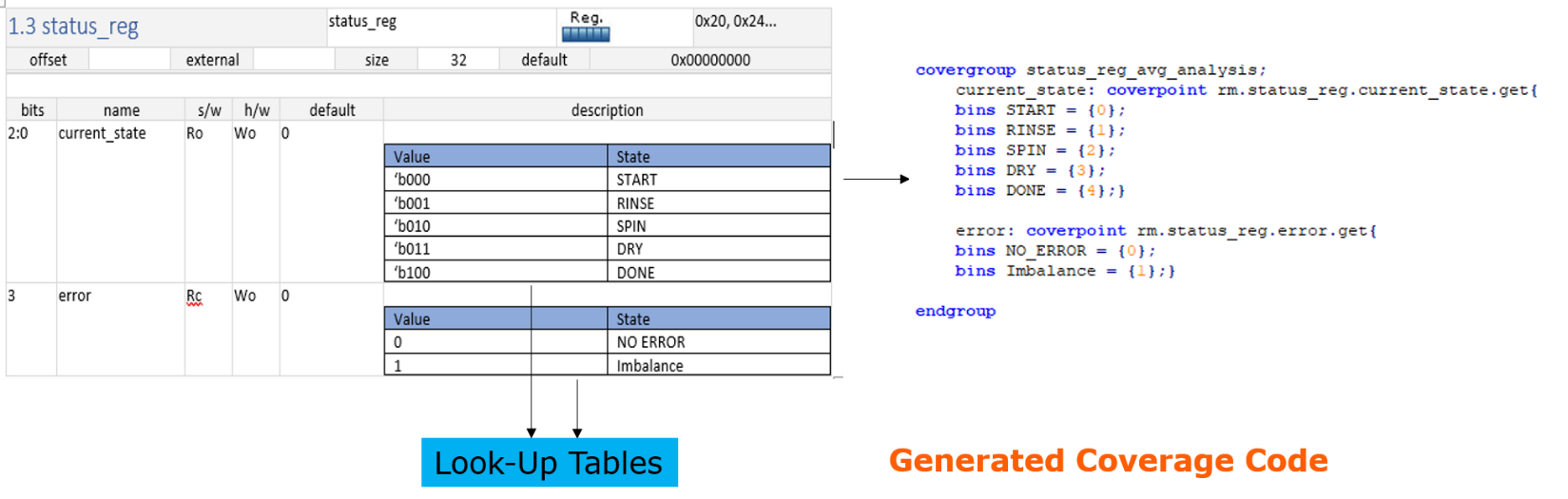

Users can also specify any commercial protocol verification IP (VIP) components in the testbench and can include any sequence specifications provided by their VIP vendors. Vendors or users can follow a similar process to specify custom functional checkers in Excel or Python. Many of the same specification features used for sequences are available for checkers. In addition, users can access callbacks and SystemVerilog interfaces, trigger on events on the buses or within the RTL, and specify assertions to check for functional correctness. Registers can be volatile, and in that case, their values need to be updated in the verification register model. To handle this, Specta-AV has a built-in Model Updater that executes “auto mirroring” whenever a hardware event occurs on a UVM register field. The automatic coverage generation process directly leverages the information contained in the register specification. For each field in each register, there is a look-up table (LUT) showing the defined values and their meaning. Specta-AV generates a SystemVerilog covergroup for each register, a coverpoint for each field, and bins for the different values. This ensures that the generated register tests exercise all meaningful field values while not artificially lowering coverage metrics due to unspecified values. In addition, Specta-AV supports cross-coverage between multiple field-level coverpoints.

Specta-AV clearly gives a big boost to verification productivity, but it benefits other teams as well. It keeps all teams in sync with a common specification. Specta-AV generates C/C++ header files for the registers, providing value to the programmers writing drivers and other software that interfaces with the hardware. The generated documentation for registers, sequences, and checkers can be used by the technical writers developing user manuals and online documentation. Perhaps the biggest value of Specta-AV is automatic updates. The register specification changes many times throughout the course of every chip project to reflect product refinement, feature changes, and impact from the implementation process. Adding or deleting a register, or even just redefining a field, might require updating testbench sequences and checkers, coverage code, software header files, and documentation. With Specta-AV, the user simply tweaks the specification and pushes a button to regenerate the output files. All project teams receive consistent updates at the same time. To learn much more about Specta-AV, including a detailed example, please view our recent webinar. |

|

|

|||||

|

|

|||||

|

|||||